L’évolution de la micro-électronique est jalonnée par le passage d’une technologie de gravure à l’autre.

Mais IBM et 3M* sur pourraient la révolutionner et donner un coup d’accélérateur sans précédent à la densité d’intégration.

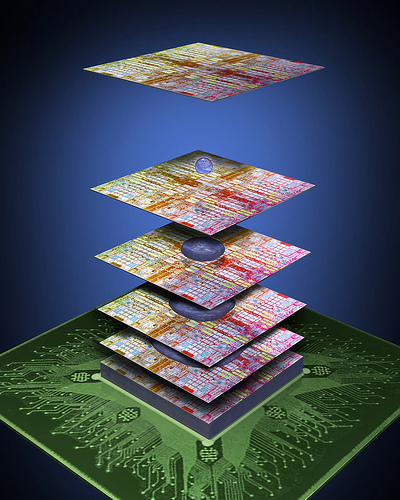

Les deux sociétés vont travailler conjointement pour développer industriellement la superposition de puces grâce à une colle spéciale.

C’est 3M qui met au point cette colle à Silicium qui permettra d’empiler des wafers (tranches) de Silicium. Il pourrait y avoir jusqu’à 100 tranches collées les unes sur les autres.

Au final, la densité d’intégration serait donc gagnée via la troisième dimension.

Les fondeurs de puces repoussent sans cesse les limites de la physique avec des procédés de lithographie et la mise en oeuvre de technologie permettant d’obtenir des transistors de plus en plus compacts.

C’est le cas avec l’utilisation d’un isolant à base de hafnium (qui est pourtant un métal) au lieu de l’oxyde de silicium pour isoler la grille des MOS (Metal Oxide Semiconductor, méthode de fabrication de composants électroniques).

Les Ivy Bridge d’Intel seront gravés dans une technologie dite 22 nm (schrink des actuels Sandy Bridge gravés en 32 nm et possible utilisation de transistors 3D).

Mais il n’en reste pas moins que les limites physiques sont tangibles et les efforts consentis pour les repousser de plus en plus lourds (en termes de coûts de fabs et de temps de développement d’une technologie).

Et quand bien même, le transistor rétrécit, le challenge est de diminuer dans les mêmes proportions les inter-connexions entre ces mêmes transistors.

Intel a déjà gagné du temps avec ses transistors MOS « 3D Tri-Gate« . Il s’agit déjà de gagner en intégration et en performance grâce à la troisième dimension.

Mais cette technologie d’Intel, dévoilée en mai 2011 et remise en avant à l’occasion de l’IDF 2011, reste basée sur les actuelles technologies planaires (MOS).

IBM et 3M vont beaucoup plus loin. Et l’empilement permettrait d’obtenir des puces bien plus denses qu’actuellement (avec un empilement de 100 puces).

« Les microprocesseurs pourraient former une ‘brique’ de silicium qui permettrait d’obtenir un CPU 1000 fois plus rapide que l’actuel plus puissant des microprocesseurs, permettant ainsi d’obtenir des smartphones, des tablettes, des ordinateurs et des consoles encore plus puissants », considère Big Blue.

Page: 1 2

Les dernières migrations de Windows 10 vers Windows 11 vont accélérer l'adoption des PC IA. Mais des…

L’IA générative excelle dans plusieurs cas d’usage, notamment dans l’analyse, la recherche et la synthèse…

Trop tôt pour envisager d'acquérir un PC Copilot+ ? Les roadmaps d'Intel et d'AMD peuvent…

Dévoilés lors du CES 2025, les PC Copilot+ au format convertible restent encore limitée dans…

Les fonctionnalités de Gemini sont intégrées dans la suite bureautique Google Workspace. Conséquence : les…

Au CES 2025, les principaux constructeurs ont annoncé l'arrivée des ordinateurs de bureau dotés de…